| Μετατροπή εσωτερικής διαφορικής απομόνωσης |  |

| Ανάλυση 16 bit | |

| Ακρίβεια: 2 γωνιακά λεπτά | |

| Έξοδος μανδάλωσης τριών καταστάσεων | |

| Υψηλή συνεχής ταχύτητα παρακολούθησης | |

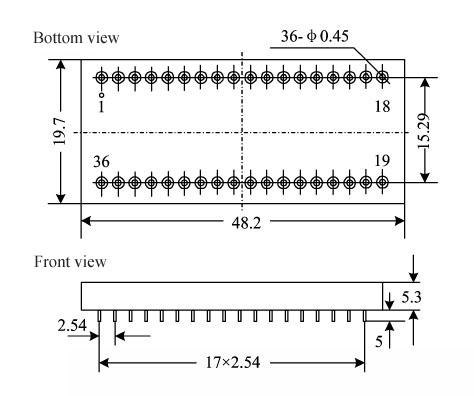

| Πακέτο DDIP με 36 σύρματα αντοχή στην ομίχλη μεταλλικό σφραγισμένο | |

| Pin-to-Pin συμβατό με Μοντέλο SDC14560 της εταιρείας DDC |

| ενσωματωμένη συσκευή μετατροπής για συνεχή παρακολούθηση σχεδιασμένη στο | αρχή του σερβομηχανισμού μοντέλου II. Τα προϊόντα αυτής της σειράς έχουν σχεδιαστεί και |

| που κατασκευάζονται με τη διαδικασία MCM, τα βασικά στοιχεία υιοθετούν ειδικό τσιπ | |

| αναπτύχθηκε ανεξάρτητα από το ινστιτούτο μας. Η διάταξη καρφίτσας είναι | |

| συμβατό με προϊόντα της σειράς SDC14560 της αμερικανικής εταιρείας DDC, 16-bit | |

| Έξοδος κλειδώματος δεδομένων παράλληλου φυσικού δυαδικού κώδικα, DIP 36 γραμμών συνολικά | |

| σφραγισμένη μεταλλική συσκευασία, έχουν τα πλεονεκτήματα της υψηλής ακρίβειας, μικρή | |

| όγκος, χαμηλή κατανάλωση ενέργειας, μικρό βάρος και υψηλή αξιοπιστία κ.λπ., | και μπορεί να χρησιμοποιηθεί ευρέως σε σημαντικά στρατηγικά και τακτικά όπλα όπως π.χ |

| αεροσκάφος, ναυτικό σκάφος, κανόνι, πύραυλος, ραντάρ, τανκ κ.λπ. | |

| 4. Ηλεκτρική απόδοση (Πίνακας 1, Πίνακας 2) | |

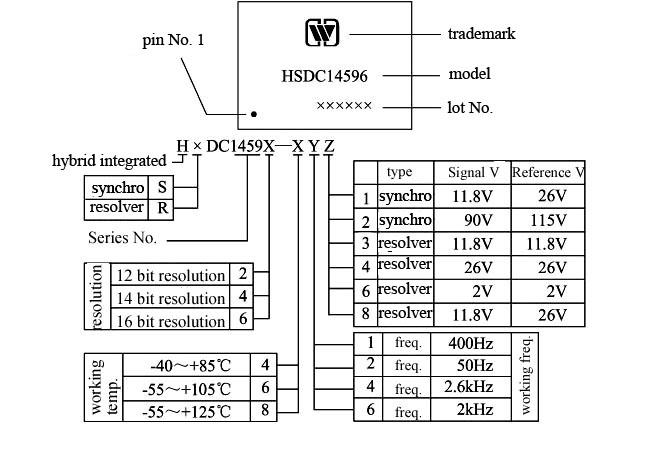

| Συγχρονισμός σε ψηφιακούς μετατροπείς ή επίλυση σε ψηφιακούς μετατροπείς (Σειρά HSDC/HRDC1459) | |

| Πίνακας 1 Βαθμολογημένες συνθήκες και προτεινόμενες συνθήκες λειτουργίας | |

| Απόλυτο μέγ. βαθμολογημένη τιμή |

| Τάση σήματος V1: ονομαστική τιμή ±20% | Τάση αναφοράς VRef: ονομαστική τιμή ±20% | Συχνότητα λειτουργίας f: ονομαστική τιμή ±20% | |

| Θερμοκρασία αποθήκευσης Tstg: -65~150℃ | Προτεινόμενες συνθήκες λειτουργίας | ||

| Λογική τάση τροφοδοσίας VL: 5±0,5V | Τάση τροφοδοσίας Vs: 15± 0,75 V | ||

| Τάση σήματος V1: ονομαστική τιμή ±10% | Τάση αναφοράς VRef: ονομαστική τιμή ±20% | Συχνότητα λειτουργίας f: ονομαστική τιμή ±20% | — |

| Εύρος θερμοκρασίας λειτουργίας (TA): -55℃~125℃ | Σημείωση: * υποδηλώνει ότι μπορεί να προσαρμοστεί σύμφωνα με τις απαιτήσεις του χρήστη. | Πίνακας 2 Ηλεκτρικά χαρακτηριστικά | Παράμετρος |

| Συνθήκες | — | Σειρά HSDC14569 | (VSu003d15V, VLu003d+5V) |

| Στρατιωτικό πρότυπο (Q/HW20725-2006) | — | 2V | Ελάχ. |

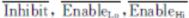

| Μέγιστη. | — | Ανάλυση | Δυαδικός παράλληλος ψηφιακός κώδικας συστήματος |

| 16 bit | — | 2V | Ακρίβεια |

| ± 10% της τάσης σήματος, τάσης αναφοράς και εύρος διακύμανσης της λειτουργίας συχνότητας | — | -2 γωνιακά λεπτά | +2 γωνιακά λεπτά |

| Εύρος συχνότητας αναφοράς | — | 50Hz | 2600 Hz |

| Εύρος τάσης αναφοράς | — | 115 V | Αντίσταση εισόδου αναφοράς |

4,4kΩ 4,4kΩ | — | 0 | 129,2 kΩ |

Εύρος τάσης σήματος Εύρος τάσης σήματος | — | 0 | 90V |

Αντίσταση εισόδου σήματος Αντίσταση εισόδου σήματος | — | 0 | 4,4kΩ |

| 102,2 kΩ | — | Μετατόπιση φάσης σήματος/αναφοράς | —70° |

| +70° | — | Λογικό επίπεδο εισαγωγής | Λογική "1" ≥3,3V |

| Λογική "0" ≤0,8V | — | εισαγωγή | 0,8V |

| εισαγωγή | — | 0,8V | |

| εισαγωγή | — | — | 0,8V |

| Λογικό επίπεδο εξόδου | — | — | Λογική "1" ≥3,3V |

| Λογική "0" ≤0,8V | — | — | Έξοδος ψηφιακού κώδικα γωνίας |

| Λογική "1" ≥3,3V | — | — | Λογική "0" ≤0,8V |

| Μετατροπή εξόδου σήματος κατειλημμένου (CB). | — | 200 δευτ | 600ns |

| Έξοδος bit ανίχνευσης σφαλμάτων | Η λογική "0" υποδηλώνει σφάλμα | — | Ικανότητα φόρτωσης |

| 3TTL | Ταχύτητα παρακολούθησης | ||

| 2,5 rps | Επιτάχυνση σταθερά | ||

| +10V Ρεύμα VSu003d+15V 10 mA |  VS u003d—15V |

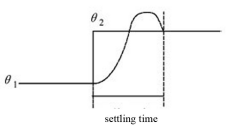

Ταχύτητα. Η διαδικασία ταλάντωσης της ψηφιακής γωνίας εξόδου φαίνεται στο

Ταχύτητα. Η διαδικασία ταλάντωσης της ψηφιακής γωνίας εξόδου φαίνεται στο 6. Αρχή λειτουργίας (Εικ. 3)

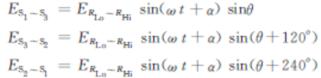

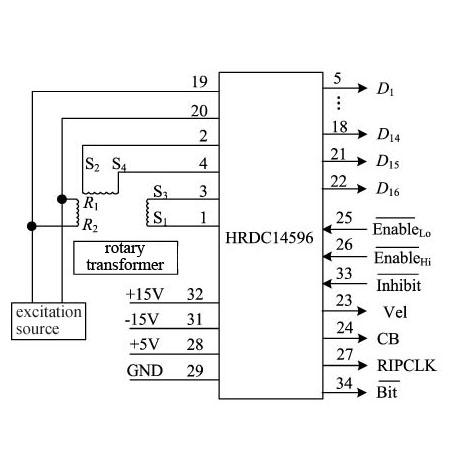

6. Αρχή λειτουργίας (Εικ. 3)| Συγχρονισμός σε ψηφιακούς μετατροπείς ή επίλυση σε ψηφιακούς μετατροπείς (Σειρά HSDC/HRDC1459) Το σήμα εισόδου του συγχρονισμού (ή αναλυτής) μετατρέπεται στο ορθογώνιο σήμα μέσω της εσωτερικής διαφορικής μόνωσης: | |

Vcosu003dKE0sin (ωt+α) cosθ (cos)ofΌπου, θ είναι η αναλογική γωνία εισόδου. Εικ. 2 Καμπύλη βήματος απόκρισης | Αυτά τα δύο σήματα και η ψηφιακή γωνία φ του εσωτερικού αντιστρέψιμου μετρητήof πολλαπλασιάζονται στον πολλαπλασιαστή των συναρτήσεων ημιτονοειδούς και συνημίτονο και είναι αντιμετωπίζεται το σφάλμα: |

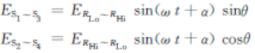

| ενίσχυση, διάκριση φάσης και διήθηση ολοκλήρωσης, αν | θ-φ≠0, ο ταλαντωτής ελεγχόμενης τάσης θα εξάγει τους παλμούς και | ο αναστρέψιμος μετρητής μετράει, έως ότου το θ-φ γίνει μηδέν εντός της ακρίβειας του | ο μετατροπέας, κατά τη διάρκεια αυτής της διαδικασίας, η μετατροπή παρακολουθεί την αλλαγή του | γωνία εισόδου όλη την ώρα. | Μέθοδος ανάγνωσης: |

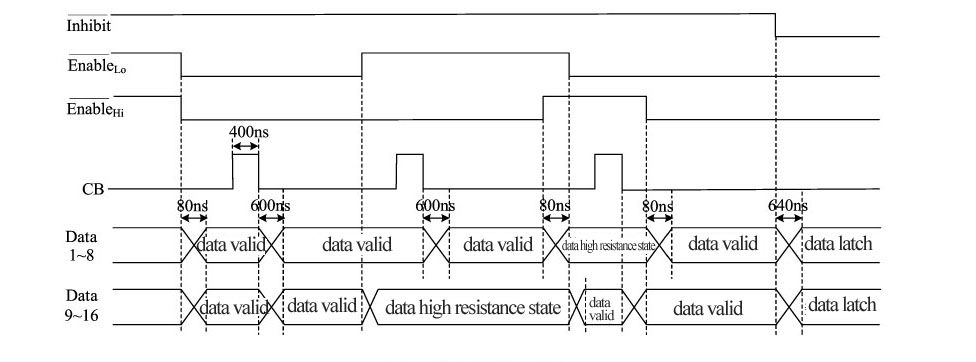

| 1 | S1 | Οι ακόλουθες δύο μέθοδοι είναι διαθέσιμες για τη μεταφορά δεδομένων: | 25 |  | (1) Μέθοδος αναστολής: |

| 2 | S2 | Μετά από 640 δευτ | 26 |  | λογική χαμηλή, τα δεδομένα εξόδου είναι έγκυρα και ο μετατροπέας πραγματοποιεί τη μεταφορά δεδομένων μέσω |

| 3 | S3 | και | 27 | . Μετά την απελευθέρωση του Inhibit , το σύστημα θα δημιουργήσει αυτόματα έναν παλμό με πλάτος ίσο με τον παλμό κατειλημμένου για ενημέρωση δεδομένων. | (2) Λειτουργία αποτομής: |

| 4 | S4 | Στην ανερχόμενη άκρη του Απασχολημένου παλμού, μετράει ο αναστρεφόμενος μετρητής τριών καταστάσεων. Στο κατερχόμενο άκρο του παλμού Απασχολημένος , εσωτερικά δημιουργεί έναν παλμό ασφάλισης με ένα πλάτος ίσο Απασχολημένο παλμό για την ενημέρωση των δεδομένων του μανδάλωσης τριών καταστάσεων, η χρονική ακολουθία των 0, 4, πώς είναι η χρονική ακολουθία των δευτερόλεπτο, στο 0, στο 0. της λογικής κατειλημμένης χαμηλή, η σταθερή μεταφορά των δεδομένων είναι έγκυρη. Στη λειτουργία ασύγχρονης ανάγνωσης, η έξοδος Απασχολημένος είναι σε επίπεδο CMOS παλμού . Το πλάτος του υψηλού και χαμηλού επιπέδου εξαρτάται από τη συχνότητα λειτουργίας και την ταχύτητα περιστροφής της επιλεγμένης συσκευής. | 28 | VL | Εικ.4 Χρονική ακολουθία μεταφοράς δεδομένων |

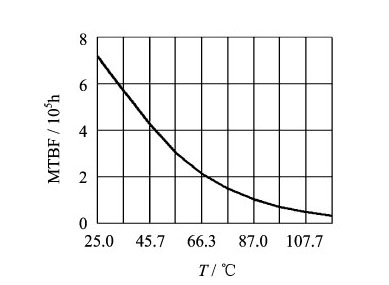

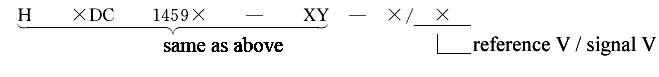

| 7. Καμπύλη MTBF (Εικ.5) | Συγχρονισμός σε ψηφιακούς μετατροπείς ή επίλυση σε ψηφιακούς μετατροπείς (Σειρά HSDC/HRDC1459) | Εικ. 5 Καμπύλη θερμοκρασίας MTBF | 29 | 8.Ορισμός καρφίτσας (Εικ.6, Πίνακας 3) | Συγχρονισμός σε ψηφιακούς μετατροπείς ή επίλυση σε ψηφιακούς μετατροπείς (Σειρά HSDC/HRDC1459) |

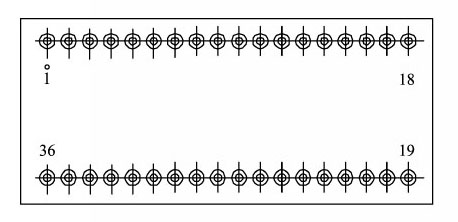

| 19 | Εικ. 6 Ορισμός καρφίτσας (Κάτω προβολή) | (Σημείωση: σύμφωνα με το GJB/Z299B-98, προβλέπεται καλή κατάσταση εδάφους) | 30 | NC | Πίνακας 3 Ορισμός καρφίτσας |

| 20 | RL | Καρφίτσα | 31 | Σύμβολο | Εννοια |

| 21 | Καρφίτσα | Σύμβολο | 32 | VS | Εννοια |

| 22 | Είσοδος επίλυσης S1 (ή εισόδου συγχρονισμού S1) | Ψηφιακός Ενεργοποιημένος έλεγχος κάτω 8 bit | 33 | Είσοδος επίλυσης S2 (ή εισαγωγή συγχρονισμού S2) | Ψηφιακός Ενεργοποιημένος έλεγχος υψηλότερων 8 bit |

| 23 | Είσοδος επίλυσης S3 (ή εισαγωγή συγχρονισμού S3) | RIPCLK | 34 | Έξοδος σήματος μηδενικών bit | Είσοδος επίλυσης S4 (αφήστε ασύνδεση) |

| 24 | CB | Τροφοδοτικό +5V | 5η 18η | NC | D1-D14 |

| Ψηφιακή έξοδος 1(MSB)-14 | GND |

| Εδαφος | Rhi |

| Είσοδος σήματος υψηλού τέλους αναφοράς | Χωρίς σύνδεση |

| RL | Είσοδος σήματος χαμηλού άκρου αναφοράς |

- VS

- VS -15V Τροφοδοσία

-15V Τροφοδοσία

D15 Ψηφιακή έξοδος 15

Ψηφιακή έξοδος 15 ).

).

Τροφοδοτικό +15 V

D16

Ψηφιακή έξοδος 16 (LSB)

Αναστέλλω

Είσοδος στατικού σήματος

Vel

S1, S2, S3, S4

S1, S2, S3, S4

Είσοδος σήματος χαμηλού άκρου αναφοράςofΠιο χαμηλα | Είσοδος σήματος με ενεργοποιημένη 8 ψηφία, αυτή η ακίδα είναι η λογική ακίδα εισόδουofέλεγχος πύλης δεδομένων, η λειτουργία του είναι να πραγματοποιεί έλεγχο τριών καταστάσεων |

|  |

| εξωτερικά στα κάτω δεδομένα εξόδου 8-bit του μετατροπέα. Χαμηλό επίπεδο είναι | ισχύει, τα κατώτερα δεδομένα εξόδου 8-bit του μετατροπέα καταλαμβάνουν τα δεδομένα |

κατάσταση αντίστασης και η συσκευή δεν καταλαμβάνει το δίαυλο δεδομένων. επιτρέπωκαι ο χρόνος καθυστέρησης απελευθέρωσης είναι 600 ns (μέγιστο). | πιο ψηλά | Είσοδος σήματος με ενεργοποιημένη 8 ψηφία, αυτή η ακίδα είναι η λογική ακίδα εισόδου | έλεγχος πύλης δεδομένων, η λειτουργία του είναι να πραγματοποιεί έλεγχο τριών καταστάσεων | εξωτερικά στα υψηλότερα δεδομένα εξόδου 8-bit του μετατροπέα. Χαμηλό επίπεδο | ισχύει, τα υψηλότερα δεδομένα εξόδου 8-bit του μετατροπέα καταλαμβάνουν τοΔίαυλος δεδομένων? Σε υψηλό επίπεδο, η ακίδα των δεδομένων εξόδου υψηλότερης 8-bit είναι σε υψηλή | κατάσταση αντίστασης και η συσκευή δεν καταλαμβάνει το δίαυλο δεδομένων. επιτρέπω | και ο χρόνος καθυστέρησης απελευθέρωσης είναι 600 ns (μέγιστο). | Αναστολή στατικής |

είσοδος σήματος, αυτή η ακίδα είναι η ακίδα εισόδου της λογικής ελέγχου, η λειτουργία της | είναι να εξάγει δεδομένα εξωτερικά στον μετατροπέα για να πραγματοποιήσει προαιρετική | Niέλεγχος μανδάλωσης ή παράκαμψης. Σε υψηλό επίπεδο, τα δεδομένα εξόδου του | Ο μετατροπέας βγαίνει απευθείας χωρίς μανδάλωμα. σε χαμηλό επίπεδο, η έξοδος | τα δεδομένα του μετατροπέα είναι κλειδωμένα, τα δεδομένα δεν ενημερώνονται, αλλά τοΟ εσωτερικός βρόχος δεν διακόπτεται, και η παρακολούθηση λειτουργεί όλο | χρόνο, το Inhibit έχει συνδέσει εσωτερικά την αντίσταση έλξης. Μετά από 600 ns (μέγιστη) καθυστέρηση του | Au κατερχόμενο άκρο του στατικού σήματος, τα δεδομένα γίνονται σταθερά (είτε το | Η συσκευή καταλαμβάνει το δίαυλο δεδομένων, δηλαδή πότε θα εξάγει τα δεδομένα εξαρτάταιγια την κατάσταση του | καιΈξοδος σήματος CB "Busy", αυτό το σήμα υποδεικνύει εάν ο δυαδικός κώδικας |

X

X