| Ολοκληρωμένο σύστημα 2 ταχυτήτων |  |

| Προγραμματιζόμενοι λόγοι ταχύτητας σε χονδρό/λεπτό κανάλι | |

| 1:8, 1:16, 1:32, 1:64 | |

| Ψηφιακή έξοδος με μάνδαλα 3 καταστάσεων | |

| Η μέγιστη ανάλυση είναι 20 bit | |

| Η μέγιστη ακρίβεια είναι 5 Arcsec |

| περιέχουν χονδρό/λεπτό αμφίδρομο συγχρονισμό σε ψηφιακό μετατροπείς ή αναλυτή σε |

|

| ψηφιακοί μετατροπείς και λογικό κύκλωμα διόρθωσης σφαλμάτων που απαιτούνται από δύο |

Οι λόγοι ταχύτητας χονδροειδούς/λεπτού συνδυασμού προϊόντων της σειράς HTS20 είναι | 1:8, 1:16, 1:32, 1:64, η απαιτούμενη αναλογία ταχύτητας μπορεί να ληφθεί με | εξωτερικό πρόγραμμα. Είναι βολικό στη χρήση. Αμφίδρομη χονδροειδής/λεπτή είσοδος Τα σήματα είναι σήματα συγχρονισμού τριών συρμάτων ή τεσσάρων καλωδίων. Φυσική έξοδος μετατροπέα SDC/RDC προγραμματιζόμενης σειράς HTS20 2 ταχυτήτων | παράλληλοι δυαδικοί κώδικες. Το μέγιστο είναι έως 20 bit. Έχουν 3 κατάσταση | μάνδαλα. | |

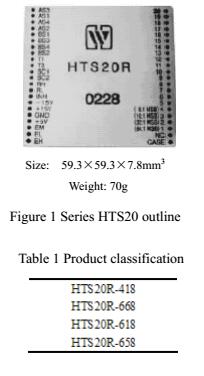

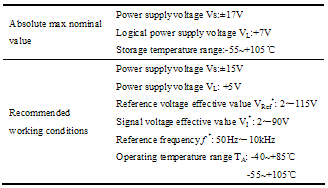

4 ΤΕΧΝΙΚΕΣ ΠΡΟΔΙΑΓΡΑΦΕΣ Μετατροπέων Synchro σε Ψηφιακό ή | Επίλυση σε ψηφιακούς μετατροπείς σειράς HTS20 Προγραμματιζόμενος SDC/RDC 2 ταχυτήτων | ||||

Μετατροπείς ( Καρτέλα 2, Καρτέλα 3 ) | Πίνακας 2 Ονομαστικές συνθήκες και προτεινόμενες συνθήκες λειτουργίας * σημαίνει ότι μπορεί να γίνει κατόπιν παραγγελίας. Πίνακας 3 Ηλεκτρικά χαρακτηριστικά Χαρακτηριστικά Συνθήκες | - - - - | 17 18 19 20 | HTS20R/HTS20S | |

Στρατιωτικό πρότυπο επιχειρήσεων | (Q/HW30925-2006) Μονάδες Σχόλια Ελάχ Μέγιστη | - - - - | 40 20 10 5 | Ανάλυση | |

(προαιρετικά ελέγχεται από SC1, SC2) αναλογία ταχύτητας 1:8 1:16 | 1:32 - - - | - 50 2 2 | 36 1:64 κομμάτι 90 | Ακρίβεια (0°~360°) Hz V V | |

|  |

10 χιλ 115 | |

,

, Επίλυση σε ψηφιακούς μετατροπείς σειράς HTS20 Προγραμματιζόμενος SDC/RDC 2 ταχυτήτων

Επίλυση σε ψηφιακούς μετατροπείς σειράς HTS20 Προγραμματιζόμενος SDC/RDC 2 ταχυτήτων Μετατροπείς (Εικ. 2, Εικ. 3)

Μετατροπείς (Εικ. 2, Εικ. 3) ,

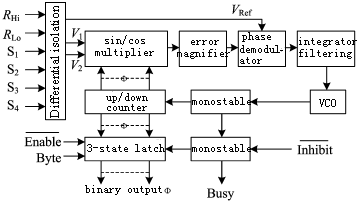

, (1) Μετατροπέας μονής ταχύτητας

(1) Μετατροπέας μονής ταχύτητας Οι αρχές λειτουργίας του μετατροπέα μονής ταχύτητας φαίνονται στο σχήμα 2, οι αρχές συνοψίζονται ως εξής:

Οι αρχές λειτουργίας του μετατροπέα μονής ταχύτητας φαίνονται στο σχήμα 2, οι αρχές συνοψίζονται ως εξής: Όπου θ είναι η αναλογική γωνία εισόδου.

Όπου θ είναι η αναλογική γωνία εισόδου. ,

, Τα δύο σήματα πολλαπλασιάζονται με την ψηφιακή γωνία φ εσωτερικής πάνω/κάτω

Τα δύο σήματα πολλαπλασιάζονται με την ψηφιακή γωνία φ εσωτερικής πάνω/κάτω .

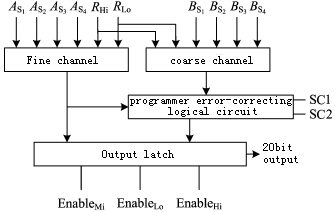

.Οι αρχές λειτουργίας του μετατροπέα 2 ταχυτήτων φαίνονται στο σχήμα 3. ο | λειτουργία του χονδροειδούς και λεπτού καναλιού του μετατροπέα 2 ταχυτήτων είναι η |

|  |

| ίδια με την προαναφερθείσα μονή ταχύτητα, αλλά ο μετατροπέας 2 ταχυτήτων αποτελείται από δύο σετ μετατροπέα μονής ταχύτητας και λογικό σφάλμα προγραμματιστή κύκλωμα. Το χοντρό κανάλι εκπληρώνει τη μετατροπή από λογική γωνία 10~12 bit | |

γωνία προς ψηφιακή γωνία. ψηφιακές γωνίες που μετατρέπονται από χοντρό κανάλι και | Τα λεπτά κανάλια εισάγονται στη λογική διόρθωσης σφαλμάτων προγραμματιστή | κύκλωμα αντίστοιχα. Μετά την επεξεργασία και τη διόρθωση σφαλμάτων, θα γίνει | εξάγετε ένα παράλληλο δυαδικό ψηφίο 20 bit, το οποίο εισάγεται στην έξοδο | μάνδαλο και προσωρινή αποθήκευση στην ψηφιακή γωνία εξόδου, εκπληρώνοντας το σύνολο | μετατροπή. | |

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 | Εικόνα 2 Λειτουργικό μπλοκ διάγραμμα Εικόνα 3 Λειτουργικό μπλοκ διάγραμμα μετατροπέα μονής ταχύτητας μετατροπέα 2 ταχυτήτων (3) Μέθοδος και χρονισμός μεταφοράς δεδομένων Οι έξοδοι των μετατροπέων 2 ταχυτήτων της σειράς HTS20 φτάνουν τα 20 bit. Διά μέσου και που αναλαμβάνουν τον έλεγχο 3 καταστάσεων του μάνταλου εξόδου, ο μετατροπέας 2 ταχυτήτων μπορεί να συνδεθεί εύκολα με το δίαυλο δεδομένων. και T1 T2 ισχύουν όλα σε χαμηλό επίπεδο. Το EnableLo ελέγχει τα χαμηλά 8 bit, το EnableMi ελέγχει τα μεσαία 8 bit, τα στοιχεία ελέγχου EnableHi τα υπόλοιπα υψηλά bit. Τα δεδομένα των μετατροπέων 2 ταχυτήτων της σειράς HTS20 διαβάζονται ως εξής: Σειρά στο λογικό "0", μετά από 490μm, τα δεδομένα στο μάνδαλο 3 καταστάσεων του μετατροπέα είναι αναβαθμίστηκε. Μπορεί να διαβάσει δεδομένα χαμηλών 8 bit, μεσαίων 8 bit και υψηλών bit μέσω του ελέγχου και Σχήμα 4 Δίνει το χρονισμό της ανάγνωσης δεδομένων όταν είναι συνδεδεμένος ο μετατροπέας 2 ταχυτήτων και ο δίαυλος δεδομένων 8 bit. Για να διασφαλίσετε τη μετατροπή υψηλής ακρίβειας του μετατροπέα 2 ταχυτήτων, δώστε προσοχή στα ακόλουθα:

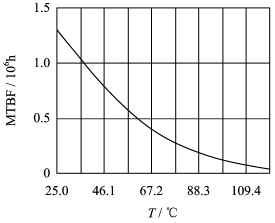

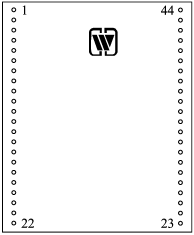

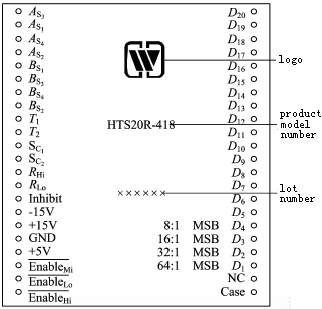

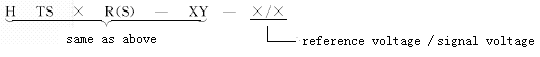

| Τα πλάτη των σημάτων εισόδου χονδροειδών και λεπτών καναλιών πρέπει να είναι εγγυημένα εντός της ονομαστικής τιμής 10%. Οι συχνότητες των σημάτων εισόδου και τα σήματα αναφοράς χονδροειδών και λεπτών καναλιών πρέπει να είναι οι καθορισμένες συχνότητες λειτουργίας. Μετατόπιση φάσης μεταξύ σήματος εισόδου και σήματος αναφοράς χονδροειδής καναλιού και φάσης μεταξύ του σήματος εισόδου και του σήματος αναφοράς του fine Το κανάλι πρέπει να είναι μικρότερο από 10°. Οι παραμορφώσεις κυμάτων των σημάτων εισόδου και των σημάτων αναφοράς χονδροειδών και λεπτών καναλιών πρέπει να είναι μικρότερες από 5%. Η διακύμανση της τροφοδοσίας +5V, ±15V πρέπει να είναι εγγυημένη εντός ±5%. 6 ΔΙΑΓΡΑΜΜΑ MTBF των μετατροπέων συγχρονισμού σε ψηφιακό ή Επίλυση σε ψηφιακούς μετατροπείς σειράς HTS20 Προγραμματιζόμενος SDC/RDC 2 ταχυτήτων Μετατροπείς (Εικ. 5) 7 ΔΙΑΜΟΡΦΩΣΕΙΣ PIN των μετατροπέων Synchro σε ψηφιακό ή Επίλυση σε ψηφιακούς μετατροπείς σειράς HTS20 Προγραμματιζόμενος SDC/RDC 2 ταχυτήτων Μετατροπείς (Εικ6, Tab4) Εικόνα 5 MTBF έναντι θερμοκρασίας Εικόνα 6 Καρφίτσωμα από πάνω ( Σημείωση: Σύμφωνα με το GJB/Z 299B-98, υποθέτοντας το έδαφος είναι σε καλή κατάσταση) Πίνακας 4 Καρφίτσωμα περιγραφής Καρφίτσα Μνημονικός Περιγραφή Καρφίτσα Μνημονικός Περιγραφή Ως 3 Ως 1 Ως 4 | 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 | Ως 2 NC Bs1 Bs3 Bs4 Bs2 D5 D6 D7 D8 D9 SC1 SC2 Rhi RLo Αναστέλλω -15V +15 V GND +5V Είσοδος λεπτού καναλιού Είσοδος λεπτού καναλιού | Είσοδος λεπτού καναλιού Είσοδος λεπτού καναλιού Είσοδος χονδροειδούς καναλιού Είσοδος χονδροειδούς καναλιού Είσοδος χονδροειδούς καναλιού Είσοδος χονδροειδούς καναλιού Πείρος ρύθμισης για μετατόπιση φάσης μεταξύ σήματος και αναφοράς Πείρος ρύθμισης για μετατόπιση φάσης μεταξύ σήματος και αναφοράς Πείρο ελέγχου προγράμματος για χοντρό και λεπτές αναλογίες ταχύτητας Πείρο ελέγχου προγράμματος για χοντρό και λεπτές αναλογίες ταχύτητας Καρφίτσα εισόδου για υψηλή αναφορά Η ακίδα εισόδου για αναφορά χαμηλή Αναστολή σήματος - Είσοδος 15 V Είσοδος +15V έδαφος Είσοδος +5V ενεργοποιήστε τα μεσαία δεδομένα 8 bit | |

,

, Δ10

Δ10 Δ11

Δ11 Δ12

Δ12 D13

D13 Δ14

Δ14

Μη συνδεδεμένο Έξοδος της υψηλότερης συνδυασμένης ψηφιακής γωνίας | Έξοδος συνδυασμένης ψηφιακής γωνίας | Έξοδος συνδυασμένης ψηφιακής γωνίας Έξοδος συνδυασμένης ψηφιακής γωνίας | Έξοδος συνδυασμένης ψηφιακής γωνίας | Έξοδος συνδυασμένης ψηφιακής γωνίας Έξοδος συνδυασμένης ψηφιακής γωνίας | Έξοδος συνδυασμένης ψηφιακής γωνίας |

Έξοδος συνδυασμένης ψηφιακής γωνίας | Έξοδος συνδυασμένης ψηφιακής γωνίας | 8 | Έξοδος συνδυασμένης ψηφιακής γωνίας | 15 | Έξοδος συνδυασμένης ψηφιακής γωνίας |

2 | Έξοδος συνδυασμένης ψηφιακής γωνίας | 9 | Έξοδος συνδυασμένης ψηφιακής γωνίας | 16 | Έξοδος συνδυασμένης ψηφιακής γωνίας |

3 | Έξοδος συνδυασμένης ψηφιακής γωνίας | 10 | Έξοδος συνδυασμένης ψηφιακής γωνίας | 17 | Έξοδος συνδυασμένης ψηφιακής γωνίας |

4 | Έξοδος συνδυασμένης ψηφιακής γωνίας | 11 | Έξοδος της λιγότερο συνδυασμένης ψηφιακής γωνίας | 18 | Σημείωση: |

5 | Το pin3,7 του HTS20S δεν είναι συνδεδεμένο. | 12 | Τα As1, As2, As3, As4 είναι είσοδος καλών καναλιών. Εάν το synchro είναι εξοπλισμένο με τρία καλώδια, το As4 δεν χρησιμοποιείται. | 19 | Τα Bs1, Bs2, Bs3, Bs4 είναι είσοδος χονδροειδών καναλιών. Εάν το synchro είναι εξοπλισμένο με τρία καλώδια, το Bs4 δεν χρησιμοποιείται. |

6 | Τα RHi, RLo είναι είσοδος σήματος αναφοράς. | 13 | Το Inhibit είναι σήμα αναστολής το οποίο συνδέεται με τροφοδοτικό 5V με pull-up αντίσταση. Όταν το Inhibit είναι λογικό "0", το εσωτερικό αναστέλλεται. Μετά από 490 δευτερόλεπτα, εξάγονται έγκυρα δεδομένα και μπορούν να διαβαστούν. Όταν είναι λογικό "1", ο μετατροπέας επαναφέρει την κατάσταση παρακολούθησης, τα δεδομένα που εξάγονται είναι μη έγκυρα δεδομένα. | 20 | Αναστέλλω |

7 | και | 14 | είναι τρεις ακίδες ελέγχου κατάστασης της εξόδου δεδομένων, οι οποίες καθόρισαν την κατάσταση |

Η θήκη είναι καρφίτσα θήκης.

Οι D1~D20 είναι έξοδοι συνδυασμένης ψηφιακής γωνίας. Το D20 είναι λιγότερο σημαντικό

κομμάτι. Όταν ο λόγος ταχύτητας είναι 1:8, το D4 είναι το πιο σημαντικό κομμάτι. Όταν η ταχύτητα | η αναλογία είναι 1:16, το D3 είναι το πιο σημαντικό κομμάτι. Όταν ο λόγος ταχύτητας είναι 1:32, D2 | είναι το πιο σημαντικό κομμάτι. Όταν ο λόγος ταχύτητας είναι 1:64, το D1 είναι το μεγαλύτερο | σημαντικό κομμάτι. ΠΙΝΑΚΑΣ ΒΑΡΟΥΣ 8 BIT των μετατροπέων συγχρονισμού σε ψηφιακό ή του αναλυτή | σε ψηφιακούς μετατροπείς σειράς HTS20 Προγραμματιζόμενος SDC ή RDC 2 ταχυτήτων Μετατροπείς ( Καρτέλα 5 ) | Πίνακας 5 Πίνακας βάρους bit | Κομμάτι | αριθμός Βάρος (μοίρες) | Κομμάτι |

αριθμός | Βάρος (μοίρες) Κομμάτι | αριθμός | Βάρος (μοίρες) | 1 (MSB) | 180.0000 1,1063 | 0,011 (40 δευτερόλεπτα) | 90.0000 |

|

|

| 45.0000 |

X

X