| Μετατροπή εσωτερικής διαφορικής απομόνωσης |  |

| Ανάλυση: 16 bit | |

| Έξοδος μάνταλου τριών καταστάσεων | |

| Αδιάλειπτη παρακολούθηση κατά τη μεταφορά δεδομένων | |

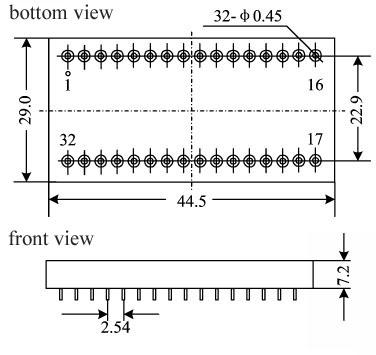

| Μεταλλική συσκευασία 32 συρμάτων |

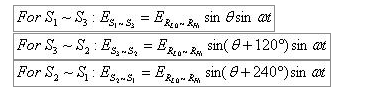

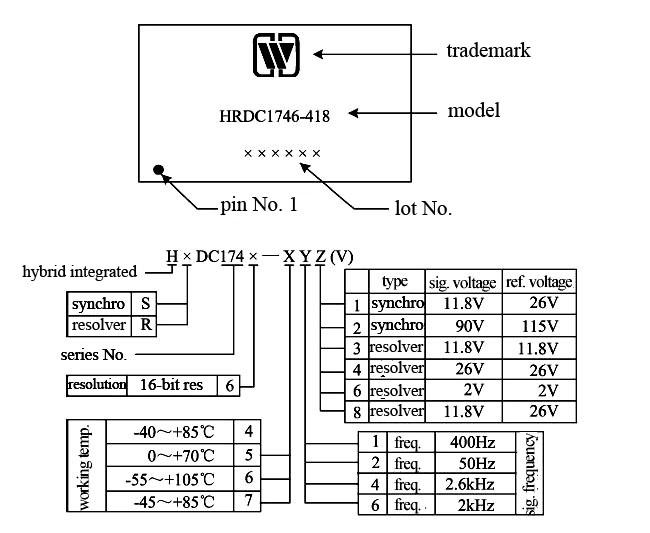

Η σειρά HSDC/HRDC1746 synchro/resolver σε ψηφιακό μετατροπέα έχει σχεδιαστεί | σχετικά με την αρχή της αρχής παρακολούθησης σερβομηχανισμού τύπου II και υιοθετεί | |||||

διαφορική είσοδο απομόνωσης, η έξοδος δεδομένων υιοθετεί μάνδαλο τριών καταστάσεων | λειτουργία, είναι κατάλληλο για μετατροπή αναλογικού/ψηφιακού σήματος | συγχρονιστής τριών συρμάτων και αναλυτής τεσσάρων συρμάτων. Με γρήγορη ταχύτητα μετατροπής | και σταθερή και αξιόπιστη απόδοση, αυτή η συσκευή μπορεί να εφαρμοστεί ευρέως στη μέτρηση γωνίας και σύστημα αυτόματου ελέγχου. | Αυτό το προϊόν κατασκευάζεται με τη διαδικασία ενσωμάτωσης υβριδικού υμενίου παχύ φιλμ και είναι | ||

Πλήρως σφραγισμένη μεταλλική συσκευασία 32 συρμάτων DIP. Τόσο το σχέδιο όσο και | ||||||

η κατασκευή του προϊόντος ικανοποιεί τις απαιτήσεις του GJB2438A-2002 | «Γενικές προδιαγραφές για υβριδικά ολοκληρωμένα κυκλώματα» και ειδικές | προδιαγραφές του προϊόντος. | ||||

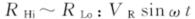

4. Ηλεκτρική απόδοση (Πίνακας 2, Πίνακας 3) | Συγχρονισμός σε ψηφιακούς μετατροπείς ή επίλυση σε ψηφιακούς μετατροπείς (Σειρά HSDC/HRDC1746) | Πίνακας 2 Βαθμολογημένες συνθήκες και προτεινόμενες συνθήκες λειτουργίας | Πίνακας 3 Ηλεκτρικά χαρακτηριστικά | Απόλυτο μέγ. ονομαστική αξία | ||

Τάση τροφοδοσίας Vs: ± 17,25 VDC | Παράμετρος | -3 | 3 | |||

HSDC/HRDC | Σειρά 1746 | 16 | ||||

Σημειώσεις | Λογική τάση τροφοδοσίας VL: +7V | 50 | Εύρος θερμοκρασίας αποθήκευσης: -55℃~150℃ | |||

Ελάχ. | Μέγιστη. | 2 | 90 | |||

Προτεινόμενες συνθήκες λειτουργίας | Τάση τροφοδοσίας Vs: ±15± 5% | 2 | Ακρίβεια/γωνιακό λεπτό | |||

| 2,6 χιλ |  |

| Μετατόπιση φάσης μεταξύ σήματος και διέγερσης:<±10% Τάση σήματος (ενεργή τιμή)/V Εύρος θερμοκρασίας λειτουργίας (TA): -40~-105℃  | |

| Τάση αναφοράς (ενεργή τιμή)/V | 115 |

| |

| προκύπτει μια συνάρτηση σφάλματος: |

Μέσω ενίσχυσης σφάλματος, διάκρισης φάσης και φιλτραρίσματος αυτούof συνάρτηση σφάλματος, προκύπτει sin(θ-φ), όταν θ-φu003d0 (εντός της ακρίβειας | του μετατροπέα), αυτό το σφάλμα θα καταστήσει ελεγχόμενη την τάσηofπαλμός διόρθωσης εξόδου ταλαντωτή για αλλαγή της δυαδικής ψηφιακής γωνίας φ |

| |

| του αντιστρέψιμου μετρητή έτσι ώστε η τιμή φ εξόδου να είναι ίση με το | εισόδου θ εντός της ακρίβειας του μετατροπέα, το σύστημα γίνεται σταθερό |

| και μπορεί να παρακολουθεί την αλλαγή της γωνίας εισόδου φ. Με αυτόν τον τρόπο, ένα δυαδικό ψηφιακό | |

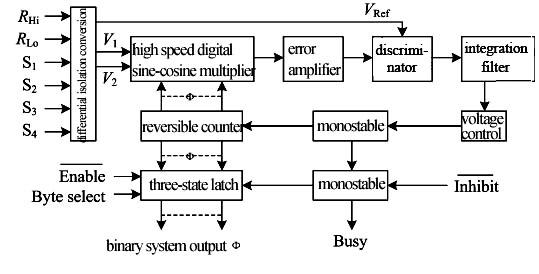

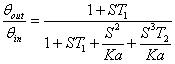

αναστρέψιμος μετρητής (Εικ. 2). | Εικ. 2 Μπλοκ διάγραμμα κυκλώματος | (1) Δυναμικά χαρακτηριστικά | Η λειτουργία μεταφοράς του μετατροπέα φαίνεται στο Σχ. 3: | Κέρδος ανοιχτού βρόχου: | Λειτουργία κλειστού βρόχου: |

1 | NC | Για τη μονάδα αυτού του μοντέλου Kau003d48000/S2, T1u003d7,1ms, T2u003d1,25ms | 17 | NC | Εικ. 3 Μεταφορά λειτουργίας του μετατροπέα |

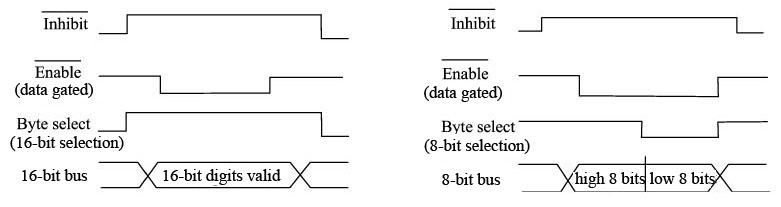

2 | D9 | (2)Μέθοδοι μεταφοράς δεδομένων και χρονική αλληλουχία | 18 | Έλεγχος επιλογής τσιπ Ενεργοποίηση | Αυτή η ακίδα είναι η ακίδα εισόδου της λογικής ελέγχου, η λειτουργία της είναι η έξοδος |

3 | δεδομένα στον μετατροπέα για την πραγματοποίηση ελέγχου τριών καταστάσεων. Χαμηλό επίπεδο είναι | ισχύει, τα δεδομένα εξόδου του μετατροπέα καταλαμβάνουν το δίαυλο δεδομένων. Όταν είναι στο | 19 | υψηλό επίπεδο, ο ακροδέκτης εξόδου δεδομένων του μετατροπέα βρίσκεται σε τρεις καταστάσεις, το | συσκευή δεν καταλαμβάνει το λεωφορείο. |

4 | Επιλογή byte | Αυτή η ακίδα είναι η ακίδα εισόδου ελέγχου, η λειτουργία της είναι να εκτελεί εξωτερικά | 20 | έλεγχος επιλογής στα δεδομένα εξόδου του μετατροπέα στη μεταφορά | λειτουργία διαύλου δεδομένων 8-bit ή διαύλου δεδομένων 16-bit. Κατά τη μεταφορά διαύλου δεδομένων 16 bit |

5 | Απαιτείται λειτουργία, κρατήστε αυτή τη λογική καρφίτσα ψηλά, τα δεδομένα θα είναι | μεταφέρεται στο δίαυλο, η έξοδος υψηλής byte βρίσκεται στον ακροδέκτη D1 έως D8 (D1 είναι | 21 | υψηλό bit) και χαμηλό byte είναι από D9 έως D16. Κατά τη μεταφορά διαύλου δεδομένων 8 bit | απαιτείται λειτουργία, τα δεδομένα λαμβάνονται στον ακροδέκτη D1 έως D8 (διατάσσονται από ψηλά |

6 | σε χαμηλό), και το υψηλό 8 bit και το χαμηλό 8 bit λαμβάνονται με δύο χρόνους | ακολουθίες, με άλλα λόγια, όταν η επιλογή Byte είναι λογική υψηλή, υψηλή 8 bit | 22 | εξάγονται και όταν είναι λογικά χαμηλό, βγαίνουν χαμηλά 8 bit. | Έλεγχος κλειδώματος δεδομένων (Σήμα αναστολής ) Αναστολή |

7 | Αυτή η ακίδα είναι η ακίδα εισόδου της λογικής ελέγχου, η λειτουργία της είναι η έξοδος | δεδομένα εξωτερικά στον μετατροπέα για να πραγματοποιηθεί η προαιρετική ασφάλιση ή παράκαμψη | 23 | έλεγχος. Σε υψηλό επίπεδο, τα δεδομένα εξόδου του μετατροπέα είναι άμεσα | έξοδος χωρίς κλείδωμα, δείτε το διάγραμμα χρονικής ακολουθίας των δεδομένων |

8 | ΜΕΤΑΦΟΡΑ. Σε χαμηλό επίπεδο, τα δεδομένα εξόδου του μετατροπέα είναι μανδαλωμένα, το | Ο εσωτερικός βρόχος δεν διακόπτεται και η παρακολούθηση εξακολουθεί να λειτουργεί | 24 | D1 | χρόνο, αλλά ο μετρητής δεν εξάγει δεδομένα. Όταν χρειάζεται για μεταφορά |

9 | δεδομένων, ο μετατροπέας κάνει πρώτα το σήμα ελέγχου Inhibit για να κλειδώσει τα δεδομένα από υψηλή σε χαμηλή, διατηρεί τη λογική χαμηλή για 640 ns και, στη συνέχεια, ορίστε το Enable input σε χαμηλό (αυτήν τη στιγμή η συσκευή καταλαμβάνει το δίαυλο δεδομένων) και στη συνέχεια | λαμβάνει δεδομένα μέσω επιλογής Byte και, στη συνέχεια, μετατρέπει όλες τις λογικές ελέγχου σε υψηλή | 25 | D2 | για να ανανεώσετε και να κλειδώσετε τα δεδομένα έτσι ώστε να ετοιμαστείτε για τη μεταφορά του |

10 | επόμενα δεδομένα, ανατρέξτε στα διαγράμματα χρονικής ακολουθίας μεταφοράς δεδομένων Εικ.4 | και Εικ.5. | 26 | D3 | (3)Μέθοδος εξασθένησης του σήματος εισόδου (Εικ.4 και Εικ.5) |

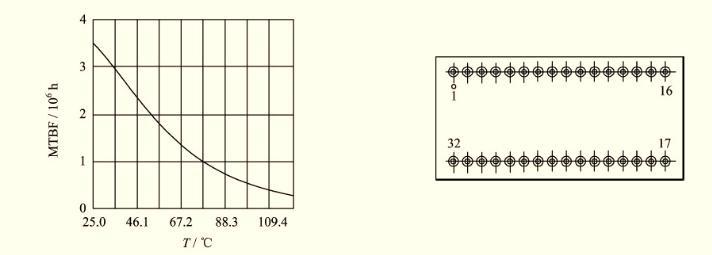

11 | Εικ. 4 Χρονική ακολουθία μεταφοράς διαύλου 16-bit | Εικ5 Χρονική ακολουθία μεταφοράς διαύλου 8-bit | 27 | D4 | 6. Καμπύλη MTBF (Εικ. 6) |

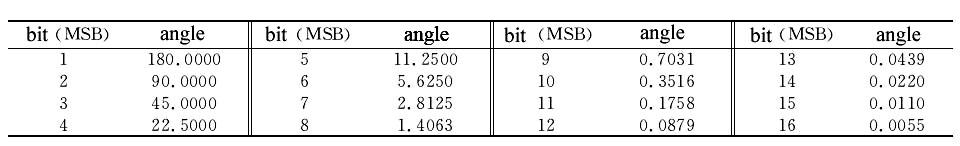

12 | Συγχρονισμός σε ψηφιακούς μετατροπείς ή επίλυση σε ψηφιακούς μετατροπείς (Σειρά HSDC/HRDC1746) | 7. Ονομασία καρφίτσας (Εικ.7, Πίνακας 4) | 28 | D5 | Συγχρονισμός σε ψηφιακούς μετατροπείς ή επίλυση σε ψηφιακούς μετατροπείς (Σειρά HSDC/HRDC1746) |

13 | S3 | Εικ.6 Καμπύλη θερμοκρασίας MTBF | 29 | D6 | Εικ. 7 Ονομασία καρφίτσας (Κάτω όψη) |

14 | S2 | (Σημείωση: σύμφωνα με το GJB/Z299B-98, προβλεπόμενη καλή κατάσταση εδάφους) | 30 | D7 | Πίνακας 4 Λειτουργική περιγραφή τερματικών ηλεκτροδίων |

15 | S1 | Καρφίτσα | 31 | D7 | Σύμβολο |

16 | NC | Εννοια | 32 | NC | Καρφίτσα |

Εδαφος | Δ12 | Ψηφιακή έξοδος για 12 bit | - VS | - Τροφοδοτικό 15 V | D13 | Ψηφιακή έξοδος για 13 bit | + VS | Τροφοδοτικό +15V |

Δ14 | Ψηφιακή έξοδος για 14 bit | Ni | Αναστέλλω | Ni | Έλεγχος κλειδώματος δεδομένων | D15 | Ψηφιακή έξοδος για 15 bit |

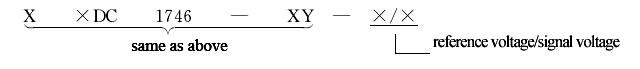

X

X